## Betriebssystembau (BSB)

### VL 5 – Unterbrechungssynchronisation

#### Alexander Krause

Lehrstuhl für Informatik 12 – Arbeitsgruppe Systemsoftware Technische Universität Dortmund

https://sys.cs.tu-dortmund.de/de/lehre/ws24/bsb

WS 24 - 29. Oktober 2024

### Agenda

Einleitung

Prioritätsebenenmodell

Harte Synchronisation

Weiche Synchronisation

Prolog/Epilog-Modell

Zusammenfassung

Referenzen

### Agenda

Einleitung

Motivation

Erstes Fazit

Prioritätsebenenmodell

Harte Synchronisation

Weiche Synchronisation

Prolog/Epilog-Modell

Zusammenfassung

Referenzen

### Motivation: Konsistenzprobleme

#### Zustandsänderungen ...

- sind Sinn und Zweck der Unterbrechungsbehandlung

- Gerätetreiber müssen über den Abschluss einer E/A Operation informiert werden

- der Scheduler muss erfahren, dass eine Zeitscheibe abgelaufen ist

- müssen mit Vorsicht durchgeführt werden

- Unterbrechungen k\u00f6nnen zu ieder Zeit auftreten

- kritisch sind Daten/Datenstrukturen, die der normale Kontrollflus

- die Unterbrechungsbehandlung sich teilen

# Beispiele aus der letzten Vorlesung

#### Beispiel 2: Ringpuffer

auch die Pufferimplementierung ist kritisch ...

```

// Pufferklasse in C++

class RoundedBuffer {

char buf[SIZE]: int occupied: int nextin, nextout:

public:

BoundedBuffer(): occupied(0), nextin(0), nextout(0) {}

void produce(char data) {

// Unterbrechungsbehandlung:

// Elementzähler merken

int elements = occupied:

if (elements == SIZE) return: // Flement verloren

// Element schreiben

buf[nextin] = data:

nextin++: nextin %= SIZE:

// Zeiger weitersetzen

occupied = elements + 1:

// Zähler erhöhen

char consume() {

// normaler Kontrollfluss:

int elements = occupied:

// Elementzähler merken

if (elements == 0) return 0: // Puffer leer. kein Ergebnis

```

// Element lesen

// Lesezeiger weitersetzen

// Ergebnis zurückliefern

// Zähler erniedrigen

4 Hinterhrechungen Software - Zustandsänderunger

char result = buf[nextout];

nextout++: nextout %= ST7F:

occupied = elements - 1:

return result:

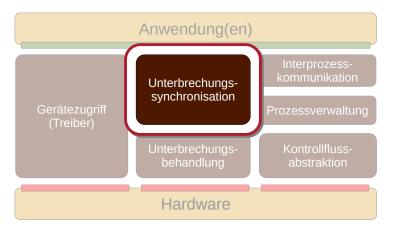

### Motivation: Ursache

Kontrollflüsse "von oben"

"begegnen" sich im Kern

und "von unten"

# Anwendungskontrollfluss (A) F\main() \www. $\mathcal{W}_{\text{consume}()}$ buf[...] **BS-Kern** $\sim$ produce() $\sim$ 4 [\handler() √

Unterbrechungskontrollfuss (UB)

### Motivation: Ursache

### Naiver Lösungsansatz

- Zweiseitige Synchronisation

- gegenseitiger Ausschluss durch Mutex, Spin-Lock, . . . (vgl. [BS])

- wie zwischen zwei Prozessen

```

Anwendungskontrollfluss (A)

Fmain()

char consume() {

mutex.lock();

₩consume()

char result = buf[nextout++];

mutex.unlock();

buf[...]

BS-Kern

return result;

void produce(char data) {

mutex.lock():

\simproduce()\sim

buf[nextin++] = data:

mutex.unlock();

4 [\handler() √

Unterbrechungskontrollfuss (UB)

```

### Naiver Lösungsansatz

- Zweiseitige Synchronisation

- gegenseitiger Ausschluss durch Mutex, Zweiseitige Synchronisation

- wie zwischen zwei Prozessen

funktioniert natürlich nicht!

```

Anwendungskontrollfluss (A)

Fmain()

char consume() {

mutex.lock();

₩consume()

char result = buf[nextout++];

mutex.unlock();

buf[...]

BS-Kern

return result:

void produce(char data) {

mutex.lock():

\simproduce()\sim

buf[nextin++] = data:

mutex.unlock():

4 Mandler() <</pre>

Unterbrechungskontrollfuss (UB)

```

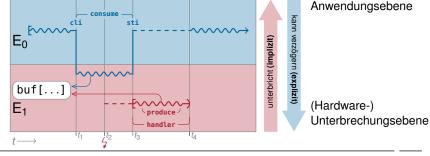

### Besserer Lösungsansatz

- Einseitige Synchronisation

- Unterdrückung der Unterbrechungsbehandlung im Verbraucher

- Operationen disable\_interrupts() enable\_interrupts() (im Folgenden o. B. d. A. in "Intel"-Schreibweise: cli() / sti())

```

Anwendungskontrollfluss (A)

```

```

Fmain()

char consume() {

cli():

√consume()√

char result = buf[nextout++];

sti():

buf[...]

BS-Kern

return result:

void produce(char data) {

// hier nichts zu tun

\simproduce()\sim

buf[nextin++] = data:

//hier nichts zu tun

4 Mandler() <</pre>

Unterbrechungskontrollfuss (UB)

```

### Besserer Lösungsansatz

- Einseitige Synchronisation

- Unterdrückung der Unterbrechungsbeh Einseitige Synchronisation

- Operationen disable\_interrupts() funktioniert. [Warum?] (im Folgenden o. B. d. A. in "Intel"-Schreibweise: cti()/sti())

```

Anwendungskontrollfluss (A)

```

```

Fmain()

char consume() {

cli():

√consume()√

char result = buf[nextout++];

sti():

buf[...]

BS-Kern

return result:

void produce(char data) {

// hier nichts zu tun

\simproduce()\sim

buf[nextin++] = data:

//hier nichts zu tun

4 Mandler() <</pre>

Unterbrechungskontrollfuss (UB)

```

### **Erstes Fazit**

- Konsistenzsicherung zwischen

- Anwendungskontrollfluss (A) und

- Unterbrechungsbehandlung (UB)

muss anders erfolgen als zwischen Prozessen

- Die Beziehung zwischen A und UB ist asymmetrisch

- Es handelt sich um "verschiedene Arten" von Kontrollflüssen

- UB unterbricht Anwendungskontrollfluss

- implizit, an beliebiger Stelle

- hat immer Priorität, läuft durch (run-to-completion)

- A kann UB unterdrücken (besser: verzögern)

- explizit, mit cli/sti (Grundannahme 5 aus VL 4)

- Synchronisation / Konsistenzsicherung erfolgt einseitig

### **Erstes Fazit**

- Konsistenzsicherung zwischen

- Anwendungskontrollfluss (A) und

- Unterbrechungsbehandlung (UB)

muss anders erfolgen als zwischen Prozessen

- Die Beziehung zwischen A und UB ist asymmetrisch

- Es handelt sich um "verschiedene Arten" von Kontrollflüssen

- UB unterbricht Anwendungskontrollfluss

- implizit, an beliebiger Stelle

- hat immer Priorität, läuft durch (run-to-completion)

- A kann UB unterdrücken (besser: verzögern)

- explizit, mit cli/sti (Grundannahme 5 aus VL 4)

- Synchronisation / Konsistenzsicherung erfolgt einseitig

#### Diese Tatsachen müssen wir beachten!

(Das heißt aber auch: Wir können sie ausnutzen)

### Agenda

### Einleitung

Prioritätsebenenmodell

Grundbegriffe

Verallgemeinerung

Konsistenzsicherung

Harte Synchronisation

Harte Synchronisation Weiche Synchronisation Prolog/Epilog-Modell Zusammenfassung Referenzen

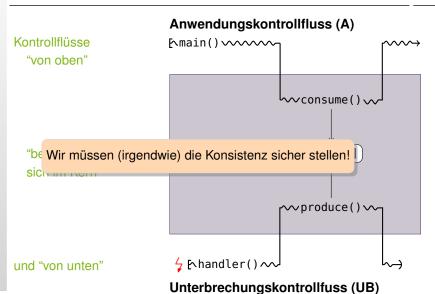

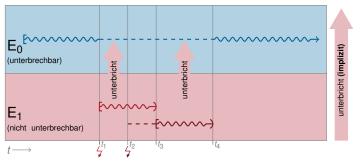

- E<sub>0</sub> sei die Anwendungskontrollfluss-Ebene (A)

- Kontrollflüsse dieser Ebene sind jederzeit unterbrechbar (durch E<sub>1</sub>-Kontrollflüsse, implizit)

- E<sub>1</sub> sei die Unterbrechungsbehandlungs-Ebene (UB)

- Kontrollflüsse dieser Ebene sind nicht unterbrechbar (durch E<sub>0/1</sub>-Kontrollflüsse, implizit)

- Kontrollflüsse derselben Ebene werden sequentialisiert

- Sind mehrere Kontrollflüsse in einer Ebene anhängig, so werden diese nacheinander abgearbeitet (run-to-completion)

- damit ist auf jeder Ebene h\u00f6chstens ein Kontrollfluss aktiv

- Die Sequentialisierungsstrategie selber ist dabei beliebig

- FIFO, LIFO, nach Priorität, zufällig, ...

- Für E<sub>1</sub>-Kontrollflüsse auf dem PC implementiert der (A)PIC die Strategie

- Kontrollflüsse können die Ebene wechseln

- Mit cli wechselt ein E<sub>0</sub>-Kontrollfluss explizit auf E<sub>1</sub>

- er ist ab dann nicht mehr unterbrechbar

- andere E<sub>1</sub>-Kontrollflüsse werden verzögert

- Mit sti wechselt ein E₁-Kontrollfluss explizit auf E₀

- er ist ab dann (wieder) unterbrechbar

- anhängige E<sub>1</sub>-Kontrollflüsse "schlagen durch"

(← Sequentialisierung)

(← Sequentialisierung)

- Verallgemeinerung für mehrere Unterbrechungsebenen:

- Kontrollflüsse auf E<sub>i</sub> werden

- jederzeit unterbrochen durch Kontrollflüsse von E<sub>m</sub>

- 2. nie unterbrochen durch Kontrollflüsse von E<sub>k</sub>

- 3. sequentialisiert mit weiteren Kontrollflüssen von E,

- Kontrollflüsse können die Ebene wechseln

- durche spezielle Operationen (hier: Modifizieren des Statusregisters)

(für m > l) (für  $k \le l$ )

### Prioritätsebenenmodell: Konsistenzsicherung

- Jede Zustandsvariable ist (logisch)

genau einer Ebene E<sub>I</sub> zugeordnet

- Zugriffe aus E<sub>1</sub> sind implizit konsistent (← Sequentialisierung)

- Konsistenz bei Zugriff aus h\u00f6heren / tieferen Ebenen muss explizit sichergestellt werden

- Maßnahmen zur Konsistenzsicherung bei Zugriffen:

- "von oben" (aus  $E_k$  mit k < I) durch harte Synchronisation

- explizit die Ebene auf E, wechseln beim Zugriff (Verzögerung)

- damit erfolgt der Zugriff aus derselben Ebene (→ Sequentialisierung)

- "von unten" (aus  $E_m$  mit m > I) durch weiche Synchronisation

- algorithmisch sicherstellen, dass Unterbrechungen nicht stören

- erfordert unterbrechungstransparente Algorithmen

### Agenda

Einleitung

Prioritätsebenenmodell

Harte Synchronisation

Ansatz

Bewertung

Weiche Synchronisation

Prolog/Epilog-Modell

Zusammenfassung

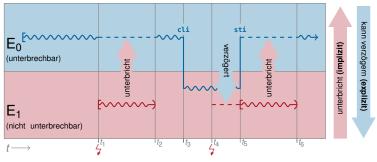

### Bounded Buffer – Lösung mit harter Synchronisation

Zugriff "von oben" wird hart synchronisiert: Für die Ausführung von consume() wechselt der Kontrollfluss auf E<sub>1</sub>

```

char consume() {

cli();

...

char result = buf[nextout++];

...

sti();

return result;

void produce

```

```

void produce(char data) {

// hier nichts zu tun

...

buf[nextin++] = data;

...

//hier nichts zu tun

}

```

Zustand liegt (logisch) auf E<sub>1</sub>

### Harte Synchronisation: Bewertung

#### Vorteile

- Konsistenz ist sicher gestellt

- auch bei komplexen Datenstrukturen und Zugriffsmustern

- unabhängig davon, was der Compiler macht

- einfach anzuwenden, "funktioniert immer"

- im Zweifelsfall legt man einfach sämtlichen Zustand auf die höchstpriore Ebene

#### Nachteile

- Breitbandwirkung

- Es werden pauschal alle Unterbrechungsbehandlungen (Kontrollflüsse) auf und unterhalb der Zustandsebene verzögert

- Prioritätsverletzung

- Es werden Kontrollflüsse höherer Priorität verzögert

- prophylaktisches Verfahren

- Nachteile werden in Kauf genommen, obwohl die Wahrscheinlichkeit, dass tatsächlich eine relevante Unterbrechung eintrifft, sehr klein ist.

### Harte Synchronisation: Bewertung (Forts.)

- Ob die Nachteile erheblich sind, hängt ab von

- Häufigkeit,

- durchschnittlicher Dauer,

- maximaler Dauer

der Verzögerung.

- Kritisch ist vor allem die maximale Dauer

- hat direkten Einfluss auf die anzunehmende Latenz

- Wird die Latenz zu hoch, können Daten verloren gehen

- edge-triggered Unterbrechungen gehen verloren

- Daten werden zu langsam von EA-Gerät abgeholt

#### **Fazit**

Harte Synchronisation ist eher **ungeeignet** für die Konsistenzsicherung **komplexer Datenstrukturen**

### Agenda

Einleitung Prioritätsebenenmodell Harte Synchronisation

Weiche Synchronisation

Ansatz

Implementierungsbeispiele

Bewertung

Prolog/Epilog-Modell Zusammenfassung Referenzen

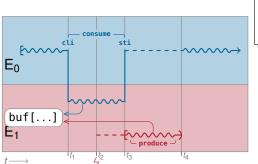

### Bounded Buffer – Ansatz mit weicher Synchronisation

Zugriff "von unten" wird weich synchronisiert: consume() liefert ein korrektes Ergebnis, auch wenn während der Abarbeitung produce() ausgeführt wurde.

### Bounded Buffer – Konsistenzbedingungen, Annahmen

- Konsistenzbedingung

- Ergebnis einer unterbrochenen Ausführung soll äquivalent sein zu dem einer sequentiellen Ausführung der Operation

- entweder consume() vor produce() oder consume() nach produce()

- Annahmen

- produce() unterbricht consume()

- alle anderen Kombinationen kommen nicht vor

- produce() läuft immer durch (run-to-completion)

### Bounded Buffer - Implementierung aus der letzten VL

### Kritisch ist der gemeinsam verwendete Zustand

```

// Pufferklasse in C++

class BoundedBuffer {

char buf[SIZE]; int occupied; int nextin, nextout;

public:

BoundedBuffer(): occupied(0), nextin(0), nextout(0) {}

void produce(char data) { // Unterbrechungsbehandlung:

int elements = occupied; // Elementzaehler merken

if (elements == SIZE) return; // Element verloren

occupied = elements + 1; // Zaehler erhoehen

// normaler Kontrollfluss:

char consume() {

int elements = occupied;  // Elementzaehler merken

if (elements == 0) return 0; // Puffer leer, kein Ergebnis

char result = buf[nextout]; // Element lesen

nextout++; nextout %= SIZE; // Lesezeiger weitersetzen

occupied = elements - 1; // Zaehler erniedrigen

// Ergebnis zurueckliefern

return result:

} };

```

### Bounded Buffer - Implementierung aus der letzten VL

### Kritisch ist der gemeinsam verwendete Zustand

```

Insbesondere Zustand, auf den

// Pufferklasse in C++

von beiden Seiten schreibend

class BoundedBuffer {

zugegriffen wird.

char buf[SIZE]; int occupied; int nextin, measure,

public:

BoundedBuffer(): occupied(0), nextin(0), nextout(0) {}

void produce(char data) { // Unterbrechungsbehandlung:

int elements = occupied: // Elementzaehler merken

if (elements == SIZE) return; // Element verloren

buf[nextin] = data;  // Element schreiben

nextin++; nextin %= SIZE; // Zeiger weitersetzen

occupied = elements + 1;

// Zaehler erhoehen

// normaler Kontrollfluss:

char consume() {

int elements = occupied; // Elementzaehler merken

if (elements == 0) return 0: // Puffer leer, kein Ergebnis

char result = buf[nextout]; // Element lesen

nextout++; nextout %= SIZE; // Lesezeiger weitersetzen

occupied = elements - 1;

// Zaehler erniedrigen

return result:

// Ergebnis zurueckliefern

} };

```

### Bounded Buffer - Alternative Implementierung

Diese alternative Implementierung kommt ohne gemeinsam beschriebenen Zustand aus.

```

// Pufferklasse in C++ (alternativ)

class BoundedBuffer {

char buf[SIZE]; int nextin, nextout;

public:

BoundedBuffer(): nextin(0), nextout(0) {}

void produce(char data) {

if ((nextin + 1) % SIZE == nextout) return;

buf[nextin] = data;

nextin = (nextin + 1) % SIZE;

char consume() {

if (nextout == nextin) return 0;

char result = buf[nextout];

nextout = (nextout + 1) % SIZE;

return result;

} };

```

### Bounded Buffer – Alternative Implementierung

```

// Pufferklasse in C++ (alternativ)

class BoundedBuffer {

char buf[SIZE]; int nextin, nextout;

public:

BoundedBuffer(): nextin(0), nextout(0) {}

void produce(char data) {

if ((nextin + 1) % SIZE == nextout) return;

buf[nextin] = data;

nextin = (nextin + 1) % SIZE;

char consume() {

if (nextout == nextin) return 0;

char result = buf[nextout]:

nextout = (nextout + 1) % SIZE;

return result;

} };

```

Allerdings gibt es hier jetzt Zustand, der von einer Seite gelesen und von der jeweils anderen beschrieben wird.

### Bounded Buffer – Alternative Implementierung

```

// Pufferklasse in C++ (alternativ)

class BoundedBuffer {

char buf[SIZE]; int nextin, nextout;

public:

BoundedBuffer(): nextin(0), nextout(0) {}

void produce(char data) {

if ((nextin + 1) % SIZE == nextout) return;

buf[nextin] = data;

nextin = (nextin + 1) % SIZE;

char consume() {

if (nextout == nextin) return 0;

char result = buf[nextout]:

nextout = (nextout + 1) % SIZE;

return result;

} };

```

Allerdings gibt es hier jetzt Zustand, der von einer Seite gelesen und von der jeweils anderen beschrieben wird.

An genau diesen Stellen müssen wir prüfen, ob die Konsistenzbedingung gilt.

### Bounded Buffer – Analyse der neuen Implementierung

buf[nextin] = data;

nextin = (nextin + 1) % SIZE;

- Angenommen, die Unterbrechung von consume() erfolgt:

- aus der Sicht von consume ()

- vor dem Lesen von nextin

- nach dem Lesen von nextin

- aus der Sicht von produce()

- vor dem Schreiben von nextout

- nach dem Schreiben von nextout

```

⇔ consume() nach produce()

⇔ consume() vor produce()

```

```

⇔ produce() vor consume()

⇔ produce() nach consume()

```

Konsistenzbedingung ist in jedem Fall erfüllt!

if ((nextin + 1) % SIZE == nextout) return;

### Systemzeit – Implementierung aus der letzten Vorlesung

```

/* globale Zeitvariable */

extern volatile time_t global_time;

/* Systemzeit abfragen */

/* Unterbrechungs-

* behandlung

time_t time () {

void timerHandler () {

return global_time;

global_time++;

h8300 - hms - q++ (16-Bit-Architektur)

time:

Problem:

mov global_time, %r0; lo

mov global_time+2, %r1; hi

Daten werden nicht

ret

atomar gelesen.

```

### Systemzeit – Konsistenzbedingungen, Annahmen, Ansatz

### Konsistenzbedingung

- Ergebnis einer unterbrochenen Ausführung soll äquivalent sein zu dem einer sequentiellen Ausführung der Operation

- entweder time() vor timerHandler() oder umgekehrt

#### Annahmen

- timerHandler() unterbricht time()

- alle anderen Kombinationen kommen nicht vor

- timerHandler() läuft immer durch (run-to-completion)

- Lösungsansatz: In time() optimistisch herangehen

- lese Daten unter der Annahme nicht unterbrochen zu werden

- 2. überprüfe, ob Annahme zutraf wurden wir unterbrochen?

- 3. falls unterbrochen, setze neu auf ab Schritt 1

### Systemzeit – Neue Implementierung

```

/* globale Zeitvariable */

extern volatile time_t global_time;

extern volatile bool interrupted;

/* Systemzeit abfragen */

/* Unterbrechungsbehandlung >

time t time () {

void timerHandler () {

time_t res;

interrupted = true;

do {

qlobal_time++;

interrupted = false;

res = global_time;

} while (interrupted);

return res;

```

Konsistenzbedingung ist nun in jedem Fall erfüllt!

### Weiche Synchronisation: Bewertung

#### Vorteile

- Konsistenz ist sichergestellt (durch Unterbrechungstransparenz)

- Priorität wird nie verletzt

- Kontrollflüsse der höherprioren Ebenen kommen immer durch

- Kosten entstehen entweder gar nicht oder nur im Konfliktfall

- gar nicht

→ Beispiel Bounded Buffer

- im Konfliktfall

optimistische Verfahren, Beispiel Systemzeit (zusätzliche Kosten durch Wiederaufsetzen)

#### Nachteile

- Lösungen häufig sehr komplex

- Wenn man überhaupt eine Lösung findet, ist diese in der Regel schwer zu verstehen – und noch schwieriger zu verifizieren

- Lösungen häufig sehr fragil (bezüglich Randbedingungen)

- Kleinste Änderungen können die Konsistenzgarantie zerstören

- Codegenerierung des Compilers ist zu beachten

- Bei größeren Datenmengen steigen die Wiederaufsetzkosten

#### Weiche Synchronisation: Bewertung (Forts.)

#### **Fazit**

- Weiche Synchronisation durch Unterbrechungstransparenz ist grundsätzlich erstrebenswert!

- Es handelt sich bei den Algorithmen jedoch immer um Speziallösungen für Spezialfälle.

- Als allgemein verwendbares Mittel für die Sicherung beliebiger Datenstrukturen ist sie nicht geeignet.

## Agenda

Einleitung

Prioritätsebenenmodell

Harte Synchronisation

Weiche Synchronisation

Prolog/Epilog-Modell

Ansatz

Implementierung

Bewertung

Zusammenfassung

## Prolog/Epilog-Modell – Motivation

- Reprise: Harte Synchronisation

- einfach, korrekt, "funktioniert immer"

- /

Hauptproblem ist die hohe Latenz

- X

- Verzögerung bei Zugriff auf den Zustand aus höheren Ebenen

- Verzögerung bei Bearbeitung des Zustands in der UB selbst

- letztlich dadurch verursacht, dass der Zustand (logisch) auf der/einer Hardwareunterbrechungsebene E<sub>1 n</sub> liegt.

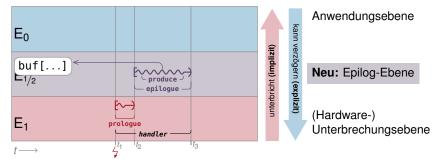

#### Prolog/Epilog-Modell – Ansatz

- Ansatz: Latenzverbergung durch zusätzliche Ebene

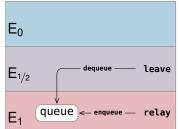

- Wir fügen eine weitere logische Ebene ein: E<sub>1/2</sub>

- $E_{1/2}$  liegt zwischen der Anwendungsebene  $E_0$  und den UB-Ebenen  $E_{1...n}$

- Unterbrechungsbehandlung wird zweigeteilt in Prolog und Epilog

- Prolog arbeitet auf Unterbrechungsebene E<sub>1...n</sub>

- Epilog arbeitet auf der neuen (Software-)Ebene E<sub>1/2</sub> (Epilogebene)

- Zustand liegt (so weit wie möglich) auf der Epilogebene

- eigentliche Unterbrechungsbehandlung wird nur noch kurz gesperrt

## Prolog/Epilog-Modell — Ansatz (Forts.)

Unterbrechungsbehandlungsroutinen werden zweigeteilt (vgl. VL6)

beginnen im Prolog (fast immer)

werden fortgesetzt im Epilog (bei Bedarf)

- Prolog (~ Hardwareunterbrechung, vgl. VL4)

- läuft auf Hardwareunterbrechungsebene

- hat damit Priorität über Anwendungsebene und Epilogebene

- ist kurz, fasst wenig oder gar keinen Zustand an

- Üblicherweise wird nur der Hardware-Zustand gesichert und bestätigt

- Unterbrechungen bleiben nur kurz gesperrt (→ Latenzminimierung)

- kann bei Bedarf einen Epilog für die weitere Verarbeitung anfordern

- **Epilog** (→ Softwareunterbrechung, vgl. SoftIRQ, VL6)

- läuft auf Epilogebene E<sub>1/2</sub> (zusätzliche Kontrollflussebene)

- Ausführung erfolgt verzögert zum Prolog

- erledigt die eigentliche Arbeit (→ Latenzverbergung)

- hat Zugriff auf größten Teil des Zustands

- Zustand wird auf Epilogebene synchronisiert

### Prolog/Epilog-Modell – Epilogebene

- Die Epilogebene wird (ganz oder teilweise)

in Software implementiert

- trotzdem handelt es sich um eine ganz normale

Prioritätsebene des Ebenenmodells

- es müssen daher auch dieselben Gesetzmäßigkeiten gelten

- Es gilt: Kontrollflüsse auf der Epilogebene E<sub>1/2</sub> werden

- 1. jederzeit unterbrochen durch Kontrollflüsse der Ebenen  $E_{1...n}$

- → Prologe (Unterbrechungen) haben Priorität über Epiloge

- 2. nie unterbrochen durch Kontrollflüsse der Ebene E<sub>0</sub>

- → Epiloge haben Priorität über Anwendungskontrollflüsse

- 3. sequentialisiert mit anderen Kontrollflüssen von  $E_{1/2}$

- $\sim$  Anhängige Epiloge werden nacheinander abgearbeitet.

- → Bei Rückkehr zur Anwendungsebene sind alle Epiloge abgearbeitet.

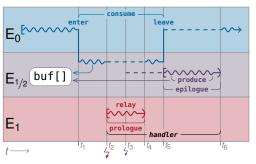

- Benötigt werden Operationen, um

- 1. explizit die Epilogebene zu betreten: enter()

- entspricht dem cli bei der harten Synchronisation

- 2. explizit die Epilogebene zu verlassen: leave()

- entspricht dem sti bei der harten Synchronisation

- 3. einen Epilog anzufordern: relay()

- entspricht dem Hochziehen der IRQ-Leitung beim PIC

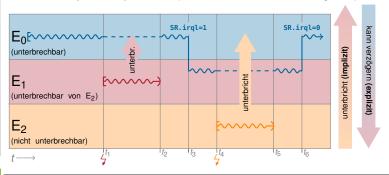

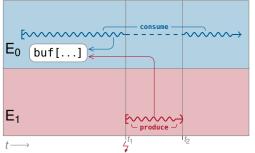

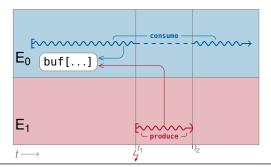

#### Prolog/Epilog-Modell – Ablaufbeispiel

E<sub>1</sub>-Unterbrechungen werden nie gesperrt.

Aktivierungslatenz der Unterbrechungsbehandlung ist minimal.

- $t_1$  Anwendungskontrollfluss betritt Epilogebene  $E_{1/2}$  (enter()).

- $t_2$  Unterbrechung  $\frac{1}{2}$  auf Ebene  $E_1$  wird signalisiert  $\longrightarrow$  Prolog wird ausgeführt.

- t<sub>3</sub> Prolog fordert Epilog für die nachgeordnete Bearbeitung an (relay() 4).

- $t_4$  Prolog terminiert, unterbrochener  $E_{1/2}$ -Kontrollfluss läuft weiter.

- $t_5$  Anwendungskontrollfluss verlässt die Epilogebene  $E_{1/2}$  (leave())  $\sim$  zwischenzeitlich aufgelaufene Epiloge werden nun abgearbeitet.

- t<sub>6</sub> Epilog terminiert, Anwendungskontrollfluss fährt auf E<sub>0</sub> fort.

- Benötigt werden Operationen, um

- 1. explizit die Epilogebene zu betreten: enter()

- entspricht dem cli bei der harten Synchronisation

- 2. explizit die Epilogebene zu verlassen: leave()

- entspricht dem sti bei der harten Synchronisation

- 3. einen Epilog anzufordern: relay()

- entspricht dem Hochziehen der IRQ-Leitung beim PIC

- Außerdem Mechanismen, um

- 4. anhängige Epiloge zu "merken": queue (z. B.)

- entspricht dem IRR (Interrupt-Request-Register) beim PIC

- 5. sicherzustellen, dass anhängige Epiloge abgearbeitet werden

- entspricht bei der harten Synchronisation dem Protokoll zwischen CPU und PIC

- Benötigt werden Operationen, um

- 1. explizit die Epilogebene zu betreten: enter()

- entspricht dem cli bei der harten Synchronisation

- 2. explizit die Epilogebene zu verlassen: leave()

- entspricht dem sti bei der harten Synchronisation

- 3. einen Epilog anzufordern: relay()

- entspricht dem Hochziehen der IRQ-Leitung beim PIC

- Außerdem Mechanismen, um

- 4. anhängige Epiloge zu "merken": queue (z. B.)

- entspricht dem IRR (Interrupt-Request-Register) beim PIC

- 5. sicherzustellen, dass anhängige Epiloge abgearbeitet werden

- entspricht bei der harten Synchronisation dem Protokoll zwischen CPU und PIC

Dieser Punkt muss etwas genauer betrachtet werden!

- 5. sicherzustellen, dass anhängige Epiloge abgearbeitet werden

- entspricht bei der harten Synchronisation dem Protokoll zwischen CPU und PIC

#### Wann müssen anhängige Epiloge abgearbeitet werden?

#### Immer unmittelbar, bevor die CPU auf E<sub>0</sub> zurückkehrt!

- 1. bei explizitem Verlassen der Epilogebene mit leave()

- während der Anwendungskrontrollfluss auf E<sub>1/2</sub> gearbeitet hat könnten Epiloge aufgelaufen sein (← Sequentialisierung).

- 2. nach Abarbeitung des letzten Epilogs

- während der Epilogabarbeitung könnten weitere Epiloge aufgelaufen sein (← Sequentialisierung).

- 3. wenn der letzte Unterbrechungsbehandler terminiert

- während der Abarbeitung von E<sub>1...n</sub>-Kontrollflüssen könnten Epiloge aufgelaufen sein (← Priorisierung).

- Implementierungsvarianten

- rein softwarebasiert

(→ Übung) (→ [1, 2])

- mit Hardwareunterstützung durch einen AST

- Ein AST (asynchronous system trap) ist eine Unterbrechung, die (nur) durch Software angefordert werden kann.

- z. B. durch Setzen eines Bits in einem bestimmten Register

- ansonsten technisch vergleichbar mit einer Hardware-Unterbrechung

- AST wird (im Gegensatz zu Traps/Exceptions) asynchron abgearbeitet

- AST läuft auf eigener Unterbrechungsebene zwischen der Anwendungsebene und den Hardware-UBs (→ unsere E<sub>1/2</sub>)

- Gesetzmäßigkeiten des Ebenenmodels gelten

(AST-Ausführung ist verzögerbar, wird automatisch aktiviert, ...)

- Sicherstellung der Epilogabarbeitung wird damit sehr einfach!

- bleibt nur noch die Verwaltung der anhängigen Epiloge

- Beispiel TriCore: Implementierung mit AST

- AST hier als Unterbrechung der E<sub>1</sub> konfiguriert (⇔ unsere E<sub>1/2</sub>)

- Geräteunterbrechungen laufen auf E<sub>2...n</sub>

```

void enter() {

CPU::setIRQL(1);

// betrete E1, verzoegere AST

void leave() {

CPU::setIRQL(0);

// erlaube AST (anhaengiger

// AST wuerde jetzt abgearbeitet)

void relay(<Epilog>) {

<haenge Epilog an queue an>

CPU_SRC1::trigger(); // aktiviere Level-1 IRQ (AST)

void __attribute__((interrupt_handler)) irg1Handler() {

while(<Epilog in gueue>) {

<entferne Epilog aus queue>

<arbeite Epilog ab>

```

- Beispiel TriCore: Implementierung mit AST

- AST hier als Unterbrechung der E<sub>1</sub> konfiguriert (⇔ unsere E<sub>1/2</sub>)

- Geräteunterbrechungen laufen auf E<sub>2...n</sub>

```

Bietet die Hardware (wie z. B. IA-

void enter() {

32) kein AST-Konzept, so kann

// be man dieses in Software nachbil-

CPU::setIRQL(1);

den.

void leave() {

CPU::setIRQL(0);

// As Näheres dazu in der Übung.

void relay(<Epilog>) {

<haenge Epilog an queue an>

CPU_SRC1::trigger(); // aktiviere Level-1 IRQ (AST)

void __attribute__((interrupt_handler)) irg1Handler() {

while(<Epilog in gueue>) {

<entferne Epilog aus queue>

<arbeite Epilog ab>

```

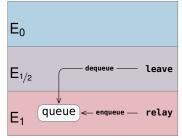

## Prolog/Epilog-Modell – Ziel erreicht?

- Kernzustand kann jetzt auf Epilogebene verwaltet und synchronisiert werden.

- Hardware-UBs müssen nicht (mehr) gesperrt werden!

- Ein Problem bleibt noch: Die Epilog-Warteschlange

- Zugriff erfolgt aus Prologen und der Epilogebene

- muss also entweder hart synchronisiert werden (im Bild)

- oder man sucht eine Speziallösung mit weicher Synchronisation

#### Prolog/Epilog-Modell – Ziel erreicht?

- Kernzustand kann jetzt auf Epilogebene verwaltet und synchronisiert werden.

- Hardware-UBs müssen nicht (mehr) gesperrt werden!

- Ein Problem bleibt noch: Die Epilog-Warteschlange

- Zugriff erfolgt aus Prologen und der Epilogebene

- muss also entweder hart synchronisiert werden (im Bild)

- oder man sucht eine Speziallösung mit weicher Synchronisation

Harte Synchronisation erscheint hier akzeptabel, da die Sperrzeit (⇔ Ausführungszeit von dequeue()) kurz und deterministisch ist.

Eine Lösung mit weicher Synchronisation (z. B. [3]) wäre natürlich schöner!

### Prolog/Epilog-Modell: Bewertung

#### Vorteile

- Konsistenz ist sichergestellt (durch Synchronisation auf Epilogebene)

- Programmiermodell entspricht dem (einfach verständlichen) Modell der harten Synchronisation

- Auch komplexer Zustand kann synchronisiert werden

- ohne das dabei Unterbrechungsanforderungen verloren gehen

- ermöglicht es, den gesamten BS-Kern auf Epilogebene zu schützen

#### Nachteile

- Zusätzliche Ebene führt zu zusätzlichem Overhead

- Epilogaktivierung könnte länger dauern als direkte Behandlung

- Komplexität für den BS-Entwickler wird erhöht

- Unterbrechungsperren lassen sich nicht vollständig vermeiden

- Gemeinsamer Zustand von Pro- und Epilog muss weiter hart oder weich synchronisiert werden

## Prolog/Epilog-Modell: Bewertung (Forts.)

#### **Fazit**

- Das Prolog/Epilog-Modell ist ein guter Kompromiss für die Synchronisation des Kernzustands.

- Es ist auch für die Konsistenzsicherung komplexer Datenstrukturen geeignet

### Agenda

Einleitung

Prioritätsebenenmodell

Harte Synchronisation

Weiche Synchronisation

Prolog/Epilog-Modell

Zusammenfassung

#### Zusammenfassung: Unterbrechungssynchronisation

- Konsistenzsicherung im BS-Kern

- muss anders erfolgen als zwischen Prozessen einseitig

- Kontrollflüsse arbeiten auf verschiedenen Prioritätsebenen

- Maßnahmen zur Konsistenzsicherung

- harte Synchronisation (durch Unterbrechungssperren)

- einfach, jedoch negative Auswirkungen auf Latenz

- Unterbrechungsanforderungen können verloren gehen

- weiche Synchronisation (durch Unterbrechungstransparenz)

- gut und effizient, jedoch nur in Spezialfällen möglich

- Implementierung kann sehr komplex werden

- Prolog/Epilog-basierte Synchronisation (Zweiteilung der Unterbrechungsbehandlung)

- guter Kompromiss

- Stand der Technik in heutigen Betriebssystemen

#### Nachtrag: Mehrkernsysteme

#### **Beachte:** Unterbrechungsbehandlung ≠ Parallelität

- Techniken funktionieren (so) nur bei echter Unterbrechungssemantik: A und UB werden auf demselben Prozessor ausgeführt

- Wird die UB "echt parallel" (auf einem weiteren Prozessor) ausgeführt, kommt es zu Problemen

- Annahmen des Prioritätsebenenmodells gelten nicht mehr! (Sequentialisierung, Priorisierung, run-to-completion)

- Asymmetrie (UB unterbricht A) ist nicht länger gegeben (weiche Synchronisation wird dadurch viel schwieriger)

- Zusätzlich erforderlich: Interprozessor-Synchronisation

- "hart" → zweiseitig blockierend, z. B. mit Spin-Locks

- → Übung

"weich" → algorithmisch nichtblockierend (schwer!)

#### Referenzen

- [1] Digital Equipment Corporation. VAX-11 Architecture Reference Manual. Document Number EK-VAXAR-RM-001. Digital Equipment Corporation. Maynard, MA, USA: Digital Press, Mai 1982.

- [2] Samuel J. Leffler, Marshall Kirk McKusick, Michael J. Karels u. a. The Design and Implementation of the 4.3 BSD UNIX Operating System. Addison-Wesley, Mai 1989. isbn: 0-201-06196-1.

- [3] Friedrich Schön, Wolfgang Schröder-Preikschat, Olaf Spinczyk u. a. "On Interrupt-Transparent Synchronization in an Embedded Object-Oriented Operating System". In: *Proceedings of the 3rd IEEE International Symposium on Object-Oriented Real-Time Distributed Computing (ISORC '00)*. Newport Beach, CA, USA: IEEE Computer Society Press, März 2000, S. 270–277. doi: http://doi.ieeecomputersociety.org/10.1109/ISORC.2000.839540.

- [BS] Peter Ulbrich. Betriebssysteme. Vorlesung mit Übung. Technische Universität Dortmund, Lehrstuhl für Informatik 12, 2021 (jährlich). url: https://sys-sideshow.cs.tu-dortmund.de/Teaching/SS2021/BS/.